Cosmo-Zの全体構成

Cosmo-Zの概要

Cosmo-ZはZYNQと高速AD変換器を搭載したデータ計測取集装置(DAQ)です。

データを計測して記録するだけではなく、計測データをFPGAのハードウェアを使ってリアルタイムかつ高速に処理することができます。FPGAのロジックとファームウェアはユーザが実験に合わせてカスタマイズすることが可能なため、ユーザの実験内容に合わせたカスタムDAQを作成することができます。

Cosmo-Zはコンパクトなサイズに多数の高速ADCチャネルを集約しており、直径90mmの円の中に最大で32chまで拡張することができます。このため、狭い空間に多数のチャネルが必要になるような実験に向いています。

Cosmo-Zの基板上にはFPGAとCPUを集約した「ZYNQ」が搭載されています。CPUはARM Cortex-A7で533MHzで動作します。このCPU上ではLinuxが動作しており、全体的な動作の管理と、Webサーバを提供しています。

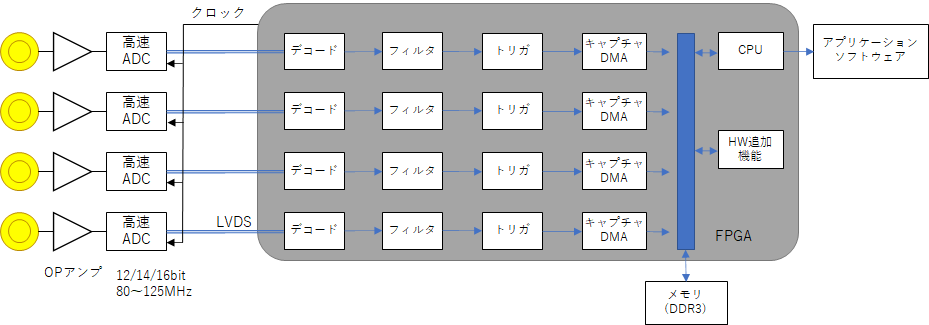

全体構成

ADCの構成

高速ADCのチャネル数は4ch (Cosmo-Z Mini)から最大32ch (Cosmo-Z TypeC基板にアナログ拡張ボードを3枚追加)となります。すべてのADCは共通のクロックで動作し、同時サンプリングされます。Cosmo-Zを複数台同期動作させることで、64ch以上への拡張も可能です。

ADCのサンプリングクロックは80MHz,100MHz,125MHzのいずれかとなります。20MHzや10MHzといった低い周波数で動作させる場合はFPGAの中でデシメーション(データを捨てること)を行います。

サンプリングチャネルは1ch~32chまで、任意の組み合わせで行うことができます。

FPGAの構成

AD変換結果はシリアル伝送でFPGAに伝えられ、FPGAでデコードされます。デコードされたデータはFPGAの中のAXI Streamバスで伝送されるので、他社のIPコアと連携したり、HLS(高レベル論理構成言語)で信号処理IPを作ることができます。

FPGAの中では計測データに対してフィルタやトリガ検出などの処理を行い、最終的に処理されたデータはキャプチャロジックによってメインメモリに格納されます。

FPGAの拡張

フィルタやトリガ検出の部分にユーザロジックを追加することでリアルタイムな信号処理機能を追加することができます。例えば、ディジタルロックインアンプや、放射線計測のためのMCA(マルチチャネルアナライザ)を作成することができます。

一方、メインメモリに格納された波形を読み出して処理するような拡張IPを開発した場合、リアルタイムではありませんが、波形処理のハードウェアアクセラレータとなります。例えば、ハードウェアFFTなどのコアがこれに該当します。

CPUの処理

CPUはFPGA内に設けられたコントロール・ステータス・レジスタを操作したり、メインメモリに格納された波形を読み書きします。

コントロール・ステータス・レジスタの操作とは、例えばADCの周波数設定や、キャプチャの開始、トリガの設定、フィルタの定数変更などを行います。

メインメモリに格納された波形はソフトウェアで読み出され、本機に内蔵されたWebサーバ上で画像化したり、SDカードに保存したり、ネットワーク上に送信したりすることができます。

メインメモリ

メインメモリは512MByteのDDR3メモリが2個搭載されていて、32bitのバスでFPGAに接続されています。メモリの動作クロックは800MHzであり、最大スループットは6.4GByte程度となります。実際にはFPGA内部のAXIバスの帯域に制限されるので4GByte程度となります。

メインメモリの1GByteのうち半分はOSが管理しており、波形用メモリとして使用できるのは512MByteとなります。ただし、OSの構成やFPGAの構成の深い部分を変更することで、OSの容量を減らしたり、より少ないメモリで動作するように割り当てを変更することは可能です。

処理能力

Cosmo-Zのメインボードの構成は125MHz 16bit 8chですが、この構成では毎秒2GByteのデータ量となるため、すべてのデータを保存することはできません。SDカードへの保存はもちろん、LAN上に送出することもできません。

したがって、FPGAのリアルタイム処理能力を生かして、イベントが発生したときだけ信号を記録したり、イベントが発生したときの波高値と時刻のみを記録するなどのデータ量削減の工夫が必要となります。データ量が毎秒1.6GByte程度まで削減できれば、連続してメインメモリに格納することができます。

メインメモリのうち波形記録用バッファに割り当てられた512MByteに納まる範囲であれば、連続して切れ目なく波形をキャプチャすることがでます。例えば、1ch 10MHzでサンプリングした場合は約25秒の連続するデータをキャプチャして保存できます。

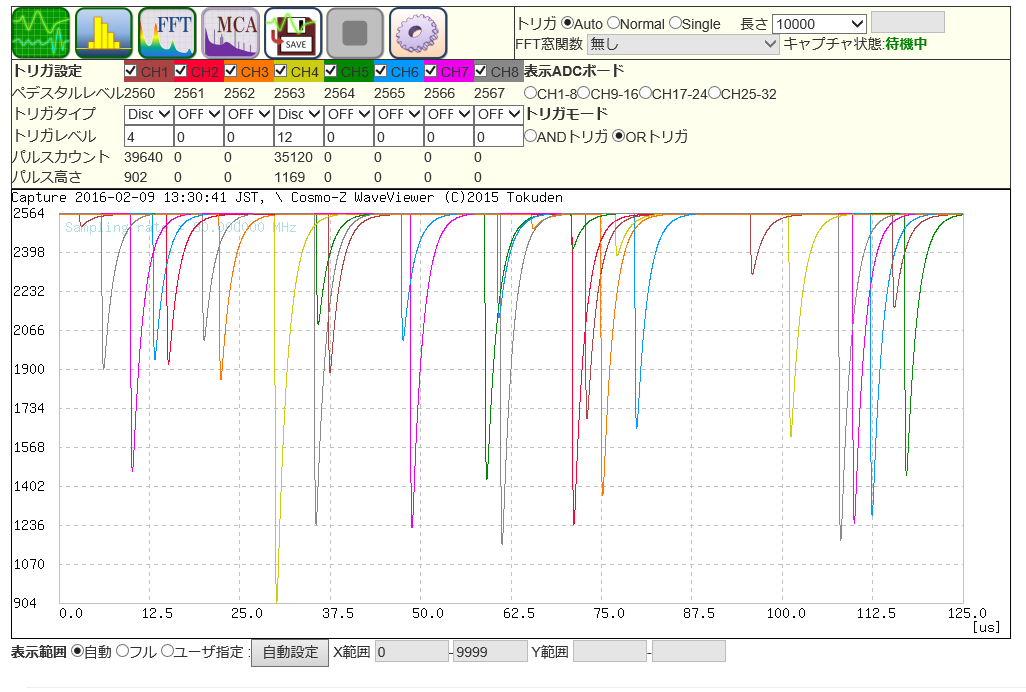

トリガ

標準では、ADCの値と閾値を比較する6種類のトリガを用意しています。

(UPPER、LOWER、RISE、FALL、Discri、Cross)

トリガの詳細についてはトリガのページをご覧ください。

上記の基本的な6種類のトリガは、計測値と閾値を比較して上回ったり下回ったりといった場合にトリガ出力を発生させるものです。アナログ的な計測回路でも類似のものは存在しています。

Cosmo-Zではユーザがオリジナルなトリガ回路を作成することができます。FPGAならではの応用例として、

- 2つ以上のシンチレータが光ったら計測開始

- 3つ以上のシンチレータが光って、パルス高さの合計値が〇〇以上なら計測開始。

といった複雑なトリガを開発することも可能です。

フィルタ回路

フィルタ回路とは狭義にはローパスフィルタやハイパスフィルタ、それを実現するためのFIRやCIRを指しますが、広義には時系列のデータを入力してデータを出力するすべての回路が該当します。

例えば、

- ゲイン・オフセット調整

- 遅延回路

- FIR/CIRフィルタ

- 放射線用の波形整形回路(TFA,BLR,CFD, Shaper)

- 波高ピーク検出回路

- 周波数検出回路

- ボックスカー積分器

- ロックインアンプ

- ディジタル変調・復調回路

- 畳み込み積分回路

- ところてん型FFT

などが、広義のフィルタとなります。

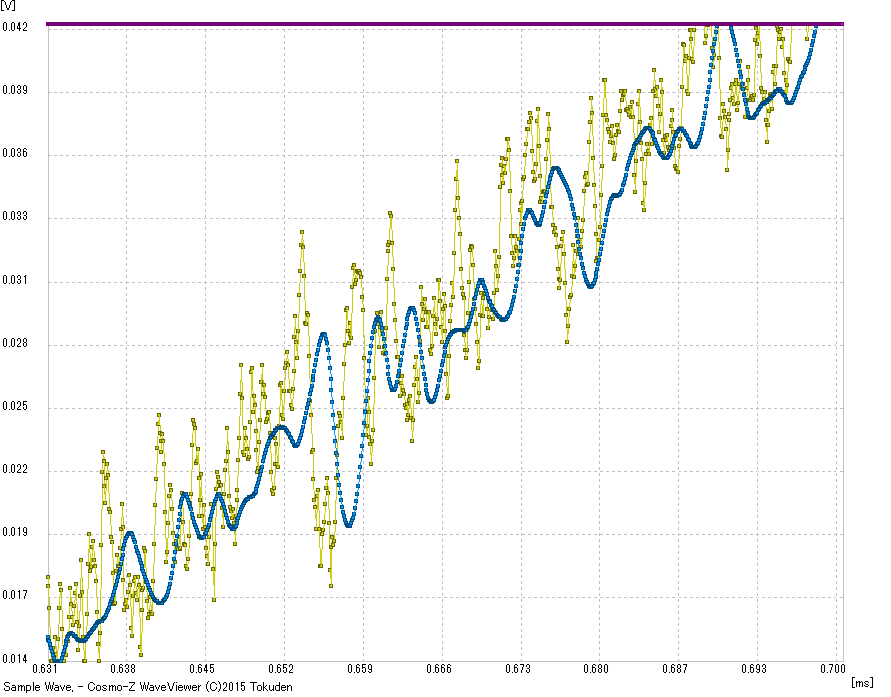

ローパスフィルタの例

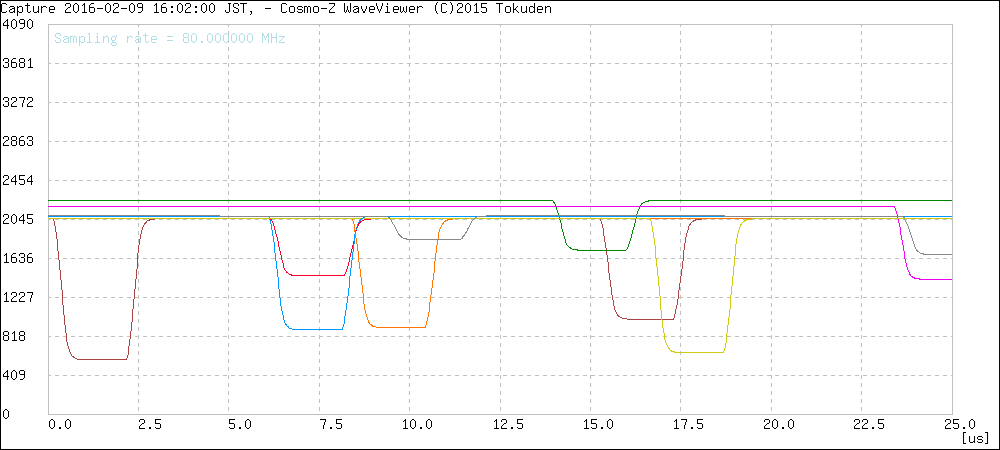

下の図はFPGAに実装したローパスフィルタの入力と出力を見たもので、黄色の線がノイズの入った入力、青い線がノイズが除去された出力です。数クロックの遅延で処理されて出てきているのがわかります。

波形整形回路の例

下の図は放射線を検出している波形の例です。放射線の波形はこのように指数関数的に減衰する波形として受信されます。

台形波形整形回路(Trapezoid Shaper)を通すと、このような波形が台形型に整形され、パイルアップに強くなるとともに弾道欠損という歪の影響を除去することができるようになります。

Trapezoid Shaperはアナログ回路では実現することができず、ディジタル信号処理のメリットが発揮されます。

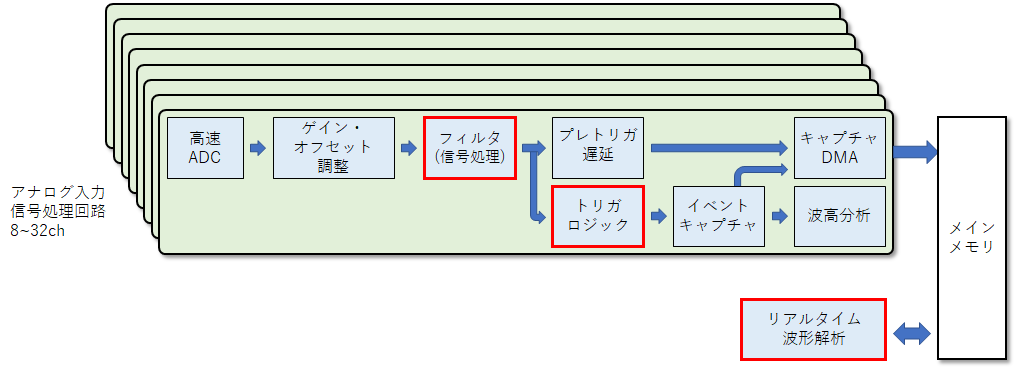

ユーザの実験に合わせたカスタマイズ

物理計測においては、どのような実験・計測でも高速ADCやDMAはだいたい同じ構成になりますが、フィルタやトリガ、波形解析のアルゴリズムはそれぞれの実験・計測の目的によりみな異なります。

そこで、Cosmo-Zではフィルタやトリガといったリアルタイム系のロジックや、メインメモリに接続して記録された波形を解析する回路をユーザが作成できるようにしています。